# A Mixed Precision Monte Carlo Methodology for Reconfigurable Accelerator Systems

Gary C.T. Chow Dept. of Computing Imperial College London SW7 2AZ, United Kingdom cchow@doc.ic.ac.uk

Wayne Luk Dept. of Computing Imperial College London SW7 2AZ, United Kingdom wl@doc.ic.ac.uk Anson H.T. Tse Dept. of Computing Imperial College London SW7 2AZ, United Kingdom htt08@doc.ic.ac.uk

Philip H.W. Leong School of Electrical and Information Engineering University of Sydney Sydney, Australia philip.leong@sydney.edu.au Qiwei Jin Dept. of Computing Imperial College London SW7 2AZ, United Kingdom qj04@doc.ic.ac.uk

David B. Thomas Dept. of Electrical and Electronic Engineering Imperial College London SW7 2AZ, United Kingdom d.thomas1@imperial.ac.uk

# ABSTRACT

This paper introduces a novel mixed precision methodology applicable to any Monte Carlo (MC) simulation. It involves the use of data-paths with reduced precision, and the resulting errors are corrected by auxiliary sampling. An analytical model is developed for a reconfigurable accelerator system with a field-programmable gate array (FPGA) and a general purpose processor (GPP). Optimisation based on mixed integer geometric programming is employed for determining the optimal reduced precision and optimal resource allocation among the MC data-paths and correction datapaths. Experiments show that the proposed mixed precision methodology requires up to 11~% additional evaluations while less than 4 % of all the evaluations are computed in the reference precision; the resulting designs are up to 7.1 times faster and 3.1 times more energy efficient than baseline double precision FPGA designs, and up to 163 times faster and 170 times more energy efficient than quad-core software designs optimised with the Intel compiler and Math Kernel Library. Our methodology also produces designs for pricing Asian options which are 4.6 times faster and 5.5 times more energy efficient than NVIDIA Tesla C2070 GPU implementations.

# **Categories and Subject Descriptors**

C.0 [Computer System Organization]: System architecture; G.1.0 [Numerical analysis]: Multiple precision arithmetic

# **General Terms**

Design, algorithms, performance

*FPGA'12*, February 22–24, 2012, Monterey, California, USA.

Copyright 2012 ACM 978-1-4503-1155-7/12/02 ...\$10.00.

## Keywords

Monte Carlo, mixed precision

### 1. INTRODUCTION

Monte Carlo (MC) simulations are a class of algorithms based on randomisation which are extensively used in many high performance computing applications in science, engineering and finance. High performance computing is often needed to solve these problems since they are computationally expensive. MC simulations are well suited to Field Programmable Gate Arrays (FPGAs), due to the parallel nature of MC algorithms and the availability of cost-effective random number generators for FPGAs. It has been shown that FPGA-based Monte Carlo applications can offer 1-2 orders of speedup over their software counterparts running on high-end CPUs [12, 21].

The ability to support customizable data-paths of different precisions is an important advantage of reconfigurable hardware. Reduced-precision data-paths usually have higher clock frequencies, consume fewer resources and offer a higher degree of parallelism for a given amount of resources compared with full precision data-paths. Although the use of reduced precision can lead to higher performance, it also affects the accuracy of the results. Most FPGA Monte Carlo designs exploit this trade-off and use data-paths that are sufficiently accurate to produce outputs within the required error tolerance [11, 17, 21]. However, when very accurate outputs are required, high precision data-paths with lower performance are unavoidable. This makes FPGAs less attractive in MC applications with high accuracy requirements.

This paper introduces a novel mixed precision methodology for accurate Monte Carlo simulations. The key difference between the proposed methodology and previous FPGA Monte Carlo designs lies in the way finite precision errors are handled. Instead of keeping the output error within a certain tolerance, the FPGA data-path is initially constructed with an aggressively reduced precision. This produces a result with finite precision error exceeding the error tolerance. An auxiliary sampling process using both a high precision reference and the reduced precision is then used to correct the error. The output accuracy of the proposed technique is not limited by the precision of the data-paths. The

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

proposed methodology can also exploit the synergy between different processors in a reconfigurable accelerator system. Reference precision computations required in the auxiliary sampling can be carried out by a general purpose processor (GPP) in a host PC, while reduced precision computations target customized data-paths on the FPGA. This allows different processors to work in precisions for which they are specialised, leading to higher overall performance.

The major contributions of this paper are:

- an error analysis that separates finite precision error and sampling error for reduced precision Monte Carlo simulations, and a novel mixed precision methodology to correct finite precision errors through auxiliary sampling (Section 2 and Section 3).

- techniques for partitioning workloads of different precisions for auxiliary sampling to a reconfigurable accelerator system consisting of FPGA(s) and GPP(s) (Section 4).

- an optimisation method based on an analytical model for the execution time of a Monte Carlo simulation on a reconfigurable accelerator system, and Mixed Integer Geometric Programming to find optimal precision for the FPGA's data-paths and optimal resource allocation (Section 5).

- evaluation of the proposed methodology using four case studies, with performance gains of 2.9 to 7.1 times speedup over FPGA only designs using double precision arithmetic. The mixed precision designs are also 44 to 163 times faster and 41 to 170 times more energy efficient compared with software design on a quad-core GPP (Section 6 and 7).

### 2. BACKGROUND

This section provides an error analysis for Monte Carlo simulations. The total error  $\epsilon_{total}$  of a Monte Carlo simulation can be divided into two components. Sampling error  $\epsilon_S$ is the error due to having a finite number of samplings and finite precision error  $\epsilon_{fin}$  is due to non-exact arithmetic. It is assumed that when a sufficiently accurate precision, such as IEEE-754 double precision, is used, the finite precision error is negligible. We call this value the **reference precision**. We also review how finite precision error is handled in related work. Let us begin with sampling error. Monte Carlo methods are used to simulate random processes and estimate the distribution of the results. Consider a sequence of mutually independent, identically distributed random variables,  $X_i$  from a MC simulation. If,  $S_N = \sum_{i=1}^N X_i$ , and the expected value, I, exists, the Weak Law of Large Numbers states that if p(x) is the probability of x, for  $\epsilon > 0$ , the approximation approaches the mean for large N [8],

$$\lim_{N \to \infty} p\left( \left| \frac{S_N}{N} - I \right| > \epsilon \right) = 0 \tag{1}$$

Moreover, if the variance  $\sigma^2$  exists, the Central Limit Theorem states that for every fixed a,

$$\lim_{N \to \infty} p\left(\frac{S_N - NI}{\sigma\sqrt{N}} < a\right) = \frac{1}{\sqrt{2\pi}} \int_{-\infty}^a e^{-z^2/2} dz \qquad (2)$$

that is, the distribution of the standard error is normal.

In practice, we must deal with finite N. If the sampling function f represents a mathematical expression defining the

quantity being sampled,  $\vec{x_i}$  is the input vector of length s from a uniform distribution  ${}^1$   $[0,1)^s$ , N is the number of sample points and  $\langle f_H \rangle_N$  is the sampled mean value of the quantity, the conventional MC sampling process<sup>2</sup> can form an approximation to I,

$$I \approx \langle f_H \rangle_N = \frac{1}{N} \sum_{i=1}^N f_H(\vec{x_i}) \tag{3}$$

Thus a sampling error  $\epsilon_S(\langle f_H \rangle_N) = I - \langle f_H \rangle_N$  with approximately normal distribution is introduced:

$$\epsilon_S(\langle f_H \rangle_N) \sim \mathcal{N}(0, \sigma_{f_H}^2/N)$$

(4)

Equation 4 shows that the bound of the sampling error can be constructed as a confidence interval. Given the same confidence level, the interval is proportional to the standard deviation of the sampling function,  $\sigma_{f_H}$ , and inversely proportional to the square root of the number of sample points, N. Hence quadrupling the number of sample points halves the confidence interval of the sampling error  $\epsilon_S(\langle f_H \rangle_N)$ . We assume there is no precision error associated with the sampling error. In FPGA designs, the sampling function f is usually evaluated using a low reduced precision,  $f_L$ , compared to the high reference precision,  $f_H$ . The reduced precision design is smaller and faster, at the expense of higher error. However, reduced precision increases the error. We call the difference between a reference precision computation and a reduced precision computation,  $f_H(x) - f_L(x)$ , the finite precision error.

Methods for dealing with finite precision error in FPGAbased MC simulations can be classified into two categories. In the first category, only standard precisions such as the IEEE single/double precision are used in sampling datapaths [10, 12]. Users are responsible for determining whether the finite precision error is acceptable, because the FPGA MC engines will follow the result of software exactly.

In the second category, error bounds of the finite precision error are constructed and the precision of the sampling datapath is adjusted such that the error bounds are smaller than the error tolerance. In [11], the maximum relative error of the sampling data-path is used to construct the error bound. The maximum relative error can be characterised using analytical methods such as interval [14] or affine arithmetic [7]. However, these approaches do not take into account that finite precision errors from different sample points might have different signs and would cancel out each other. Hence there is usually an over-estimation of finite precision error in Monte Carlo simulation.

In [17], test runs with a pre-defined number of sample points are used to empirically estimate the maximum percentage error due to finite precision effect empirically. The finite precision error of MC simulations using the same datapath and the same number of sample point are then assumed to share the same error bound. This assumption is not al-

<sup>&</sup>lt;sup>1</sup>Some MC simulations require non-uniformly distributed  $\vec{x}$  values, for example in many option pricing simulations normally distributed  $\vec{x}_i$  are required.

<sup>&</sup>lt;sup>2</sup>Throughout the paper, we use the subscript H and L to denote quantities evaluated with the reference precision arithmetic and the reduced precision arithmetic respectively. We use  $\langle X \rangle$  to denote the sampled mean value of a random variable X and  $\langle X \rangle_N$  to denote the sampled mean value of X calculated by N samples.

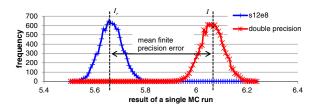

Figure 1: Distribution of 10k runs of a reduced precision and a double precision Monte Carlo.

ways valid and thus the empirical error bound can only be used as a reference rather than a rigorous bound.

In [18], a design is proposed with both high precision and reduced precision data-paths for computing cumulative distribution functions (CDFs). The two CDFs are compared using a Kolmogorov-Smirnov test, the distance score of which is then used to control the precision of the reduced precision data-path adaptively such that finite precision error is within the range of error tolerance.

In [4] a mixed-precision approach for comparison is presented. It is different from this work since it does not involve MC simulation.

The benefits for reduced precision designs are well-known. For instance, it has been shown [5] that appropriate wordlength optimisation can improve the area of adaptive filters and polynomial evaluation circuits by up to 80%, power reduction of up to 98%, and speed of up to 36% over common alternative design strategies. This research shows that impressive gains can also be obtained by exploiting reduced precision for complex designs supporting Monte Carlo simulation.

#### 3. MIXED PRECISION METHODOLOGY

Our novel mixed precision methodology is motivated by two ideas. First, we can correct the finite precision error when both its magnitude and sign are known. Second, in Monte Carlo simulations, we are only interested in the finite precision error in the final result but not the finite precision errors of individual sample points.

When a reduced precision data-path is used in a Monte Carlo simulation, the reduced precision expected value  $I_r$  is approximated by the following equation, where  $N_L$  is the number of sample points:

$$I_r \approx \langle f_L \rangle_{N_L} = \frac{1}{N_L} \sum_{i=1}^{N_L} f_L(\vec{x_i})$$

(5)

Due to the effect of finite precision error, the reduced precision sample mean  $\langle f_L \rangle_N$  cannot be used to approximate the expected value I directly as I might not equal to  $I_r$ . We define the difference of the two expected means as the mean finite precision error,  $\mu_{\epsilon_{fin}}$ , where

$$\mu_{\epsilon_{fin}} = I - I_r \tag{6}$$

Figure 1 shows the distributions of Monte Carlo simulations using a reduced precision  $(s12e8)^3$  data-path and a double precision data-path of for pricing Asian options. In each MC simulation, N = 32,768 sample points are used and each of the reduced and double precision MC simulation is

repeated for 10,000 times with different random seeds. As shown in the figure, the magnitude of the mean finite precision error  $\mu_{\epsilon_{fin}}$  between the expected value of I and  $I_r$  is significant. When reduced precision data-paths are used for the Monte Carlo simulation without the correction by the auxiliary sampling, the true value of the simulation will lie within  $\pm \mu_{\epsilon_{fin}}$  of the sampled value. Moreover, this uncertainty cannot be reduced by increasing the number of sample points and is a fundamental limit of conventional reduced precision MC simulations.

To find both the magnitude and the signs of the mean finite precision error  $\mu_{\epsilon_{fin}}$ , we define an auxiliary sampling function  $f_a(\vec{x})$ :

$$f_a(\vec{x}) = f_H(\vec{x}) - f_L(\vec{x}) = \epsilon_{fin}(\vec{x}) \tag{7}$$

where  $\epsilon_{fin}$  is the finite precision error for each  $\vec{x}$ . With a sufficient large sample size  $N_a$ , we can approximate the mean finite precision error  $\mu_{\epsilon_{fin}}$ :

$$\mu_{\epsilon_{fin}} \approx \langle f_a \rangle_{N_a} = \frac{1}{N_a} \sum_{i=1}^{N_a} f_a(\vec{x_i}) \tag{8}$$

The sampling error of this auxiliary sampling  $\epsilon_S(\langle f_a \rangle_{N_a}) = \mu_{\epsilon_{fin}} - \langle f_a \rangle_{N_a}$  is approximately normal distributed:

$$\epsilon_S(\langle f_a \rangle_{N_a}) \sim \mathcal{N}(0, \sigma_{f_a}^2 / N_a) \tag{9}$$

Finally, we can approximate the true mean I by two sets of sampling:

$$I_{mixed} = \langle f_L \rangle_{N_L} + \langle f_a \rangle_{N_a} \tag{10}$$

$$E(I_{mixed}) = E(\langle f_L \rangle_{N_L}) + E(\langle f_a \rangle_{N_a})$$

=  $I_r + (I - I_r) = I$  (11)

As shown in Equation 11, the expected value of the auxiliary sampling is  $I - I_r$ . Hence the expected mean of the mixed precision approximation  $I_{mixed}$  is exactly the same as the expected mean I computed in the reference precision. Equation 10 can thus be viewed as the reduced precision sample mean plus a correction for the mean finite precision error.

Since two samplings are used in the proposed mixed precision methodology, there are two sampling errors in the result and they can be found using Equation 13 and 14. As both sampling errors are approximately normally distributed, their sum is also approximately normally distributed and has a variance equal to the sum of their individual variances as shown in Equation 15 if uncorrelated random numbers are used. By using the proposed mixed precision methodology, we effectively replace the finite precision error of reduced precision data-paths by the sampling error of the auxiliary sampling. A confidence interval can also be constructed using the combined variance.

$$\epsilon_S(I_{mixed}) = \epsilon_S(\langle f_L \rangle_{N_L}) + \epsilon_S(\langle f_a \rangle_{N_a}) \tag{12}$$

$$\epsilon_S(\langle f_L \rangle_{N_L}) \sim \mathcal{N}(0, \sigma_{f_L}^2 / N_L)$$

(13)

$$\epsilon_S(\langle f_a \rangle_{N_a}) \sim \mathcal{N}(0, \sigma_{f_a}^2/N_a)$$

(14)

$$\sigma_S(I_{mixed}) \sim \mathcal{N}(0, \sigma_{f_L}^2/N_L + \sigma_{f_a}^2/N_a)$$

(15)

Although the proposed mixed precision methodology is analysed mathematically, we also show its desired effect through experiments. Using Equation 15, we find that a mixed precision MC run using a precision of s12e8 with  $N_a = 1078$  and

6

<sup>&</sup>lt;sup>3</sup>In this paper, we use the notation sAeB to denote a floating point representation, where A is the number of significand bits and B is the number of exponent bits.

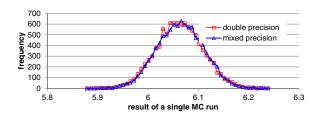

Figure 2: Distribution of 10k runs of a mixed precision and a double precision Mont Carlo.

$N_L = 33,773$  should yield the same error as a double precision sampling with N = 32,768. We repeat both the mixed precision and the double precision MC 10,000 times using different random seeds, and their distributions are shown in Fig. 2. Note that both distributions have roughly the same variance and mean. The result agrees with our mathematical model and no finite precision error exists between the double precision Monte Carlo and our mixed precision Monte Carlo runs.

The proposed mixed precision methodology provides several advantages over previous FPGA designs.

- 1. The final result is adjusted with an approximated mean finite precision error  $\mu_{e_{fin}}$ . This is a novel approach which enables us to obtain a more accurate result from the reduced precision result instead of passively finding the error bound.

- 2. Since there are only sampling errors in the output, we can achieve very accurate result by increasing the number of sample points  $N_L$  and  $N_a$ . The output accuracy is no longer limited by the reduced precision.

- 3. The methodology is applicable to any Monte Carlo simulation because no accuracy analysis is required for the relative error and the methodology is totally independent of the function f.

Although the proposed mixed precision methodology enables us to aggressively exploit reduced precision data-paths while maintaining the accuracy of the final result using auxiliary sampling, each auxiliary sampling still requires a costly evaluation of the sampling function f at the reference precision.

The effectiveness of the proposed technique depends heavily on how resources are allocated among the reduced precision hardware and auxiliary sampling hardware. To find the optimal resource allocation, we should consider a number of factors such as the cost of evaluating  $f_L$  and  $f_H$ , the area available on the FPGA, the bandwidth between the FPGA and GPP, and the reduced precision values being used.

In the next section, we propose different schemes for partitioning workloads. An analytical model is developed in Section 5 based on the partitioning schemes which enables us to find the optimal resource allocation and optimal reduced precision using mixed integer geometric programming.

### 4. WORKLOAD PARTITIONING

General-purpose processors (GPPs) are optimised for standard precisions such as IEEE-754 single/double precision. GPPs can also employ reduced precision via multiple precision software libraries such as MPFR [9]. Multiple standard precision instructions are required to complete a reduced precision computation even if the reduced precision format

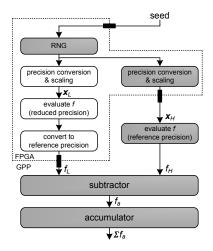

Figure 3: Reduced precision sampling data-path.

Figure 4: Workload partitioning of the auxiliary sampling. States in reference precision are shaded.

has a smaller wordlength. Hence, it is usually not cost effective to use GPPs for reduced precision computations. On the other hand, FPGA data-paths are customizable. Lower precision are usually preferred over higher precision ones because they usually have higher clock frequency, consume less resources and allow higher degrees of parallelism given the same amount of resources. It is thus better to perform reduced precision computations on the FPGA and leave reference precision computations to the GPP.

Since the sampling of  $\langle f_L \rangle_{N_L}$  involves only reduced precision evaluations of f, we assume it is achieved by using reduced precision sampling data-paths on FPGA as shown in figure 3. A seed is fed into the random number generator from the GPP. The random numbers are converted into the reduced precision format and scaled to the sampling domain. Although only a small fraction of bits generated by the RNG are used in reduced precision sampling, we keep the bit-width of the RNG the same as that for reference precision sampling. The scaled random number is then evaluated by the reduced precision sampling function evaluator. The accumulation is performed in reference precision to avoid loss of accuracy due to insufficient dynamic range in the accumulator. Finally, the accumulated result is sent back to the GPP. Multiple reduced precision sampling data-paths can be used with different seeds, and the averaging of the final results is done in the GPP.

Figure 4 shows the workload partitioning of the auxiliary sampling. It consists of 4 main stages: (1) random number generation, (2) evaluation of the sampling function f in reference and reduced precision, (3) computing the difference ebetween  $f_L$  and  $f_H$  in reference precision, and (4) accumulation of the difference. Auxiliary sampling is the process used to estimate the average finite precision error  $(\mu_{\epsilon_{fin}})$  between the reduced and the reference precision data-paths under the same set of random inputs. We implement the random number generator using the FPGA and sent results back to the GPP. This method utilises highly efficient RNG generation on FPGAs which are an order of magnitudes faster than GPP based RNGs [16]. The trade-off for this partitioning method is increased bandwidth. For each sample point of the auxiliary sampling, we need to transfer s reference precision random numbers and one reference precision evaluation result from the FPGA to the GPP where s is the dimension of the sampling function.

| $ \begin{array}{c} \sigma_{tol} & \mbox{output error tolerance, in terms of standard deviation of the output ation of the output s dimension of the sampling function \\ \sigma_{f_L} & \mbox{standard deviation of reduced precision sampling } \\ \sigma_{f_a} & \mbox{standard deviation of auxiliary sampling } \\ L & \mbox{the number of significand bits being used in the reduced precision data-paths } \\ \hline P_L \in \mathbb{Z} & \mbox{number of reduced precision sampling data-paths } \\ \hline P_{aux} \in \mathbb{R} & \mbox{effective number of auxiliary sampling data-paths } \\ \hline P_{GA} & \mbox{parameters (for each FPGA) } \\ \hline A_{total} & \mbox{total available area } \\ A_{com} & \mbox{cost of communication infrastructure } \\ R_S & \mbox{slack ratio } \\ freq & \mbox{clock frequency } \\ c & \mbox{number of clock cycles to compute a sample point } \\ \hline A_{red} & \mbox{cost of a areduced precision sampling data-paths as } \\ \hline BPP & \mbox{parameters } \\ \hline T_{aux} & \mbox{time required to compute a sample point } \\ \hline System parameters \\ \hline N_{core} & \mbox{number of GPPs in the system } \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Problem parameters              |                                                  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|--|--|--|--|--|--|--|--|

| ation of the outputsation of the outputsdimension of the sampling function $\sigma_{f_L}$ standard deviation of reduced precision sampling $\sigma_{f_a}$ standard deviation of auxiliary samplingLthe number of significand bits being used in the<br>reduced precision data-paths $p_L \in \mathbb{Z}$ number of reduced precision sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $realcost of communication infrastructureR_Sslack ratiofreqclock frequencycnumber of clock cycles to compute a sample pointA_{red}cost of a reduced precision sampling data-paths asshown in figure 3A_{aux}cost of auxiliary sampling data-pathGPP parametersGPP parametersT_{aux}time required to compute a sample pointN_{core}number of cores in each GPPnumber of GPPs in the system$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | *                               |                                                  |  |  |  |  |  |  |  |  |

| $\begin{array}{lll} s & \mbox{dimension of the sampling function} \\ \sigma_{f_L} & \mbox{standard deviation of reduced precision sampling} \\ \sigma_{f_a} & \mbox{standard deviation of auxiliary sampling} \\ L & \mbox{the number of significand bits being used in the} \\ & \mbox{reduced precision data-paths} \\ \hline & \mbox{Resource allocation parameters} \\ \hline & \mbox{Resource allocation parameters} \\ \hline & \mbox{reduced precision sampling data-paths} \\ \hline & \mbox{effective number of auxiliary sampling data-paths} \\ \hline & \mbox{effective number of auxiliary sampling data-paths} \\ \hline & \mbox{FPGA parameters (for each FPGA)} \\ \hline & \mbox{A}_{total} & \mbox{total available area} \\ \hline & \mbox{cost of communication infrastructure} \\ \hline & \mbox{Rs} & \mbox{slack ratio} \\ \hline & \mbox{freq} & \mbox{clock frequency} \\ \hline & \mbox{cost of a reduced precision sampling data-paths} \\ \hline & \mbox{GPP parameters} \\ \hline & \mbox{GPP parameters} \\ \hline & \mbox{GPP parameters} \\ \hline & \mbox{System parameters} \\ \hline & \mbox{N}_{core} & \mbox{number of GPPs in the system} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\sigma_{tol}$                  |                                                  |  |  |  |  |  |  |  |  |

| $\begin{array}{ll} \sigma_{f_L} & \mbox{standard deviation of reduced precision sampling} \\ \sigma_{f_a} & \mbox{standard deviation of auxiliary sampling} \\ L & \mbox{the number of significand bits being used in the} \\ reduced precision data-paths & \mbox{mesource allocation parameters} \\ \hline & \mbox{Resource allocation parameters} & \mbox{mesource allocation parameters} & \mbox{paux} \in \mathbb{R} & \mbox{effective number of auxiliary sampling data-paths} \\ \hline & \mbox{paux} \in \mathbb{R} & \mbox{effective number of auxiliary sampling data-paths} & \mbox{FPGA parameters (for each FPGA)} & \mbox{A}_{total} & \mbox{total available area} & \mbox{cost of communication infrastructure} & \mbox{stack ratio} & \mbox{freq} & \mbox{clock frequency} & \mbox{commute of a colock cycles to compute a sample point} & \mbox{A}_{red} & \mbox{cost of a areduced precision sampling data-paths} & \mbox{shown in figure 3} & \mbox{A}_{aux} & \mbox{cost of auxiliary sampling data-path} & \mbox{GPP parameters} & \mbox{T}_{aux} & \mbox{time required to compute a sample point} & \mbox{System parameters} & \mbox{N}_{core} & \mbox{number of GPPs in the system} & \mbox{mumber of GPP} & \mbox{mumber of GPPs in the system} & \mbox{mumber of GPS} & mum$                                                                                                                                                                           | 0                               | 1                                                |  |  |  |  |  |  |  |  |

| $\begin{array}{c c} \sigma_{f_a} \\ \sigma_{f_a} \\ L \\ the number of significand bits being used in the reduced precision data-paths \\ \hline Resource allocation parameters \\ \hline Resource allocation parameters \\ \hline P_L \in \mathbb{Z} \\ number of reduced precision sampling data-paths \\ \hline p_{aux} \in \mathbb{R} \\ \hline effective number of auxiliary sampling data-paths \\ \hline FPGA parameters (for each FPGA) \\ \hline A_{total} \\ A_{total} \\ total available area \\ A_{com} \\ cost of communication infrastructure \\ R_S \\ slack ratio \\ freq \\ clock frequency \\ c \\ number of clock cycles to compute a sample point \\ \hline A_{red} \\ cost of a reduced precision sampling data-paths as shown in figure 3 \\ \hline A_{aux} \\ \hline GPP parameters \\ \hline T_{aux} \\ \hline time required to compute a sample point \\ \hline System parameters \\ \hline N_{core} \\ N_{gpp} \\ number of GPPs in the system \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                               |                                                  |  |  |  |  |  |  |  |  |

| $\begin{array}{c c} L & \mbox{the number of significand bits being used in the reduced precision data-paths} \\ \hline & \mbox{Resource allocation parameters} \\ \hline & \mbox{Resource allocation parameters} \\ \hline & \mbox{Resource allocation parameters} \\ \hline & \mbox{paux} \in \mathbb{R} & \mbox{effective number of auxiliary sampling data-paths} \\ \hline & \mbox{FPGA parameters (for each FPGA)} \\ \hline & \mbox{A}_{total} & \mbox{total available area} \\ \hline & \mbox{A}_{com} & \mbox{cost of communication infrastructure} \\ \hline & \mbox{R}_{S} & \mbox{slack ratio} \\ \hline & \mbox{freq} & \mbox{clock frequency} \\ \hline & \mbox{c} & \mbox{number of clock cycles to compute a sample point} \\ \hline & \mbox{Cost of a arcluced precision sampling data-paths as} \\ \hline & \mbox{shown in figure 3} \\ \hline & \mbox{A}_{aux} & \mbox{cost of auxiliary sampling data-path} \\ \hline & \mbox{GPP parameters} \\ \hline & \mbox{T}_{aux} & \mbox{time required to compute a sample point} \\ \hline & \mbox{System parameters} \\ \hline & \mbox{N}_{core} & \mbox{number of GPPs in the system} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |                                                  |  |  |  |  |  |  |  |  |

| reduced precision data-pathsResource allocation parameters $p_L \in \mathbb{Z}$ number of reduced precision sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $p_{aux} \in \mathbb{R}$ effective number of auxiliary sampling data-paths $A_{total}$ total available area $A_{com}$ cost of communication infrastructure $R_S$ slack ratio $freq$ clock frequency $c$ number of clock cycles to compute a sample point $A_{red}$ cost of a reduced precision sampling data-paths as<br>shown in figure 3 $A_{aux}$ cost of auxiliary sampling data-pathGPP parameters $T_{aux}$ time required to compute a sample point $N_{core}$ number of cores in each GPP<br>number of GPPs in the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 | Ja                                               |  |  |  |  |  |  |  |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |                                                  |  |  |  |  |  |  |  |  |

| $\begin{array}{c c} p_L \in \mathbb{Z} \\ p_{aux} \in \mathbb{R} \end{array} & \mbox{number of reduced precision sampling data-paths} \\ \hline p_{aux} \in \mathbb{R} \end{array} & \mbox{effective number of auxiliary sampling data-paths} \\ \hline FPGA parameters (for each FPGA) \\ \hline A_{total} \\ A_{com} \\ cost of communication infrastructure \\ R_S \\ slack ratio \\ freq \\ cost of cock frequency \\ c \\ number of clock cycles to compute a sample point \\ A_{red} \\ cost of a reduced precision sampling data-paths as \\ shown in figure 3 \\ A_{aux} \\ cost of auxiliary sampling data-path \\ \hline GPP parameters \\ \hline T_{aux} \\ time required to compute a sample point \\ System parameters \\ \hline N_{core} \\ N_{gpp} \\ number of GPPs in the system \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |                                                  |  |  |  |  |  |  |  |  |

| $\begin{array}{ll} p_{aux} \in \mathbb{R} & \text{effective number of auxiliary sampling data-paths} \\ \hline & FPGA \ parameters (for each FPGA) \\ \hline & A_{total} & total available \ area \\ \hline & A_{com} & cost \ of \ communication \ infrastructure \\ \hline & R_S & slack \ ratio \\ \hline & freq & clock \ frequency \\ \hline & c & number \ of \ clock \ cycles \ to \ compute \ a \ sample \ point \\ \hline & A_{red} & cost \ of \ auxiliary \ sampling \ data-paths \ as \\ \hline & A_{aux} & cost \ of \ auxiliary \ sampling \ data-path \\ \hline & GPP \ parameters \\ \hline \hline & T_{aux} & time \ required \ to \ compute \ a \ sample \ point \\ \hline & System \ parameters \\ \hline & N_{core} & number \ of \ GPPs \ in \ the \ system \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 | *                                                |  |  |  |  |  |  |  |  |

| $ \begin{array}{c c} \hline & \ & \ & \ & \ & \ & \ & \ & \ & \ &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |                                                  |  |  |  |  |  |  |  |  |

| $\begin{array}{c} A_{total} \\ A_{com} \\ Cost of communication infrastructure \\ R_S \\ S \\ Slack ratio \\ freq \\ clock frequency \\ c \\ number of clock cycles to compute a sample point \\ Cost of a reduced precision sampling data-paths as shown in figure 3 \\ A_{aux} \\ Cost of auxiliary sampling data-path \\ \hline CPP \ parameters \\ T_{aux} \\ T_{aux} \\ T_{aux} \\ Core \\ number of cores in each GPP \\ number of GPPs in the system \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $p_{aux} \in \mathbb{R}$        |                                                  |  |  |  |  |  |  |  |  |

| $\begin{array}{rcl} A_{com} & \mbox{cost of communication infrastructure} \\ R_S & \mbox{slack ratio} \\ freq & \mbox{clock frequency} \\ c & \mbox{number of clock cycles to compute a sample point} \\ A_{red} & \mbox{cost of a reduced precision sampling data-paths as} \\ hown in figure 3 \\ A_{aux} & \mbox{cost of auxiliary sampling data-path} \\ \hline & \mbox{GPP parameters} \\ \hline T_{aux} & \mbox{time required to compute a sample point} \\ \hline & \mbox{System parameters} \\ \hline N_{core} & \mbox{number of cores in each GPP} \\ number of GPPs in the system \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FPGA parameters (for each FPGA) |                                                  |  |  |  |  |  |  |  |  |

| $\begin{array}{rl} R_S & {\rm slack\ ratio} \\ freq & {\rm clock\ frequency} \\ c & {\rm number\ of\ clock\ cycles\ to\ compute\ a\ sample\ point} \\ A_{red} & {\rm cost\ of\ a\ reduced\ precision\ sampling\ data-paths\ as} \\ A_{aux} & {\rm cost\ of\ auxiliary\ sampling\ data-path} \\ \hline & {\rm GPP\ parameters} \\ \hline T_{aux} & {\rm time\ required\ to\ compute\ a\ sample\ point} \\ \hline & {\rm System\ parameters} \\ \hline N_{core} & {\rm number\ of\ GPPs\ in\ the\ system} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $A_{total}$                     | total available area                             |  |  |  |  |  |  |  |  |

| $ \begin{array}{rcl} freq & \mbox{clock frequency} \\ c & \mbox{number of clock cycles to compute a sample point} \\ A_{red} & \mbox{cost of a reduced precision sampling data-paths as} \\ shown in figure 3 \\ A_{aux} & \mbox{cost of auxiliary sampling data-path} \\ \hline & \mbox{GPP parameters} \\ \hline T_{aux} & \mbox{time required to compute a sample point} \\ \hline & \mbox{System parameters} \\ \hline N_{core} & \mbox{number of cores in each GPP} \\ number of GPPs in the system \\ \hline \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $A_{com}$                       | cost of communication infrastructure             |  |  |  |  |  |  |  |  |

| $ \begin{array}{c} c \\ A_{red} \\ A_{red} \\ A_{red} \\ cost of a reduced precision sampling data-paths as shown in figure 3 \\ A_{aux} \\ cost of auxiliary sampling data-path \\ \hline \\ GPP \ parameters \\ \hline \\ T_{aux} \\ \hline \\ T_{aux} \\ \hline \\ Frequired to \ compute \ a \ sample \ point \\ \hline \\ System \ parameters \\ \hline \\ N_{core} \\ N_{gpp} \\ number \ of \ GPPs \ in \ the \ system \\ \hline \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $R_S$                           | slack ratio                                      |  |  |  |  |  |  |  |  |

| $\begin{array}{c} A_{red} \\ A_{red} \\ A_{red} \\ Cost of a reduced precision sampling data-paths as shown in figure 3 \\ A_{aux} \\ Cost of auxiliary sampling data-path \\ \hline \\ GPP \ parameters \\ \hline \\ T_{aux} \\ T_$ | freq                            | clock frequency                                  |  |  |  |  |  |  |  |  |

| $ \begin{array}{c} \text{shown in figure 3} \\ \hline A_{aux} & \text{cost of auxiliary sampling data-path} \\ \hline & & & & & \\ \hline & & & & \\ \hline & & & & \\ \hline T_{aux} & \text{time required to compute a sample point} \\ \hline & & & & \\ \hline & & & & \\ \hline & & & & \\ \hline & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | c                               | number of clock cycles to compute a sample point |  |  |  |  |  |  |  |  |

| $\begin{array}{c} A_{aux} & {\rm cost \ of \ auxiliary \ sampling \ data-path} \\ & {\rm GPP \ parameters} \\ \hline T_{aux} & {\rm time \ required \ to \ compute \ a \ sample \ point} \\ \hline System \ parameters \\ \hline N_{core} & {\rm number \ of \ cores \ in \ each \ GPP} \\ N_{gpp} & {\rm number \ of \ GPPs \ in \ the \ system} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $A_{red}$                       | •                                                |  |  |  |  |  |  |  |  |

| GPP parameters $T_{aux}$ time required to compute a sample point           System parameters         System parameters $N_{core}$ number of cores in each GPP $N_{gpp}$ number of GPPs in the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 1 0 1                         |                                                  |  |  |  |  |  |  |  |  |

| $T_{aux}$ time required to compute a sample point         System parameters       System parameters $N_{core}$ number of cores in each GPP $N_{gpp}$ number of GPPs in the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $A_{aux}$                       | cost of auxiliary sampling data-path             |  |  |  |  |  |  |  |  |

| System parameters $N_{core}$ number of cores in each GPP $N_{gpp}$ number of GPPs in the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GPP parameters                  |                                                  |  |  |  |  |  |  |  |  |

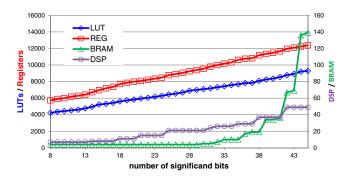

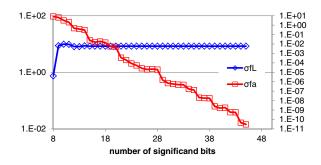

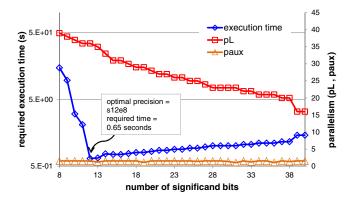

| $ \begin{array}{c} N_{core} \\ N_{gpp} \end{array} \text{ number of GPPs in the system} \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $T_{aux}$                       | time required to compute a sample point          |  |  |  |  |  |  |  |  |